# BNL-101839-2014-TECH AD/RHIC/RD/57;BNL-101839-2013-IR

## Direct Digital Phase Shift by DDS rf Source

A. Pei

April 1993

Collider Accelerator Department

Brookhaven National Laboratory

### **U.S. Department of Energy**

USDOE Office of Science (SC)

Notice: This technical note has been authored by employees of Brookhaven Science Associates, LLC under Contract No.DE-AC02-76CH00016 with the U.S. Department of Energy. The publisher by accepting the technical note for publication acknowledges that the United States Government retains a non-exclusive, paid-up, irrevocable, world-wide license to publish or reproduce the published form of this technical note, or allow others to do so, for United States Government purposes.

### **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or any third party's use or the results of such use of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof or its contractors or subcontractors. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

### RHIC PROJECT

Brookhaven National Laboratory

Direct Digital Phase Shift by DDS rf Source

Alex Pei

### Direct Digital Phase Shift by DDS Rf Source

#### Alex Pei

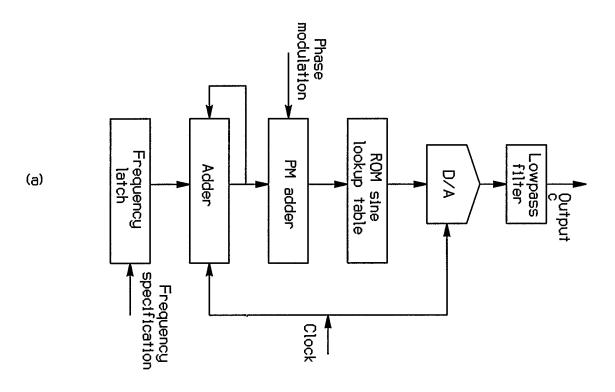

As direct digital synthesizers with built-in high resolution digital phase modulator become available (eg. Stanford Telecom's STEL-75 series), it is possible to use the digital phase modulation function to replace conventional analog phase shifters in many accelerator applications. A block diagram of such a synthesizer is shown in Fig.1(a).

Other than saving additional parts which results in lower cost and higher reliability, there is a wide array of additional benefits.

Wideband phase-shifting is automatically guaranteed by the digital phase-modulator. In the analog scheme, unless a signal is originally obtained in quadrature format, precise 90 degree phase shifter has to be used. Although much progress have been made in recent years, it is still difficult to have very wide band operation of 90 degree phase splitting.

Another critical component, the analog multiplier, is also eliminated. The amplitude dependence and overall linearity of an analog phase shifter depend on the precision of both the 90 degree phase splitting and the multiplication operation. Thus with the digital PM inside DDS, the overall linearity is improved and there is no parasitic amplitude modulation.

The analog trig function generator chips used in the analog phase shifters are both precise and easy to use. However, its range is limited to  $\pm 2\pi$ , resulting in a phase shifter that has the same range limitation. In the digital direct synthesizers, we can let the PM register overflow. By  $2\pi$  modulus of the PM register, the correct phase value will be automatically reached by the phase table warping. This extended range is particularly useful in locking two rf systems of different frequencies in which division of phase by rational

numbers is involved.

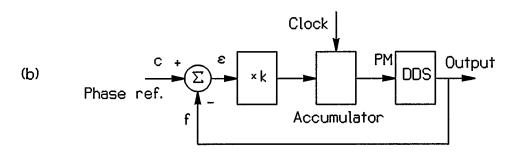

Fig.1 (a): Block diagram of DDS with phase modulation. (b): A simple phase lock feedback system employing such a DDS.

The following is a discussion of design approaches using built-in DDS PM.

The DDS PM register is interfaced with an accumulator. The accumulator's function is much the same as an integrator in analog circuits. It can be described by the following difference equation:

$$y(n)=y(n-1)+x(n-1)$$

(1)

where x and y are input and output of the accumulator respectively. The quantity n and n-1 corresponds to the nth and (n-1)th clock of the system.

For a simple system that requires phase lock to a reference, we have the block diagram of Fig.1(b).

If the control is steady, the error signal will have the following homogeneous difference equation:

$$\varepsilon(n+1) + (k+1)\varepsilon(n) = 0 \tag{2}$$

whose solution is:

$$\varepsilon(n) = C (1-k)^n \tag{3}$$

where C is an initial condition dependent constant.

We thus see that for 0 < k < 2 the system is stable. The convergence or the speed of the loop can be adjusted by varying the coefficient k.

A general loop can include cavities and other delay elements. The difference

equations will be more complicated and the z transform and bilinear transformation from s to z domain are useful tools.