# BNL-101838-2014-TECH AD/RHIC/RD/56;BNL-101838-2013-IR

Numerically Controlled Phase Locked Loop Using Direct Digital Synthesizer

A. Pei

April 1993

Collider Accelerator Department Brookhaven National Laboratory

## **U.S. Department of Energy**

USDOE Office of Science (SC)

Notice: This technical note has been authored by employees of Brookhaven Science Associates, LLC under Contract No.DE-AC02-76CH00016 with the U.S. Department of Energy. The publisher by accepting the technical note for publication acknowledges that the United States Government retains a non-exclusive, paid-up, irrevocable, world-wide license to publish or reproduce the published form of this technical note, or allow others to do so, for United States Government purposes.

### DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or any third party's use or the results of such use of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof or its contractors or subcontractors. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

## AD/RHIC/RD-56

## RHIC PROJECT

# Brookhaven National Laboratory

## Numerically Controlled Phase Locked Loop Using Direct Digital Synthesizer

Alex Pei

April 1993

.

## Numerically Controlled Phase Locked Loop Using Direct Digital Synthesizer

#### Alex Pei

A direct digital synthesizer is a highly stable digitally controlled frequency generator that outputs high spectrum purity rf signals. Because of the all digital design, it is immune to various environmental disturbances (mechanical, temperature, etc) that plague conventional LC based VCOs. As a result, a PLL based on DDS can achieve high spectrum purity with very narrow tracking bandwidth.

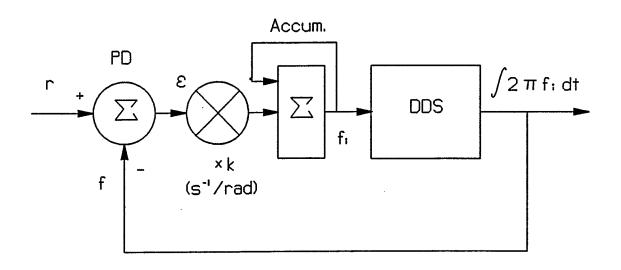

A basic concept of phase locked loop based on the direct digital synthesizer is shown in Fig.1. The output of the direct digital synthesizer is compared to the reference signal phase r by a phase comparator. The phase error signal  $\epsilon$  is scaled by a multiplier k and is added to an accumulator. The accumulator in turn directly controls the frequency  $f_i$  of the DDS. With the frequency controlled by a phase error signal, the DDS output phase is the time integration of the input of the DDS. The whole system is updated by a clock with a period of  $\Delta T$ . The PLL is essentially a discrete digital system with a sampling period of  $\Delta T$ .

To evaluate the performance of such a system, let's denote n as the nth system clock and write down the difference equations.

1

#### Fig.1 Block diagram of a digital PLL with DDS

The DDS output, which is also the feedback signal f, is the integration of the error signal and can be written as:

$$f(n) = f(n-1) + 2\pi \Delta T A(n-1)$$

<sup>(1)</sup>

The accumulator is characterized by the following difference equation:

$$A(n) = A(n-1) + k\varepsilon(n-1)$$

<sup>(2)</sup>

The error signal at the nth clock is simply

- - - -

. . .

$$\varepsilon(n) = r(n) - f(n)$$

=  $r(n) - [f(n-1) + 2\pi \Delta T A(n-1)]$

=  $r(n) - r(n-1) + \varepsilon(n-1) - 2\pi \Delta T [A(n-2) + k\varepsilon(n-2)]$  (3)

Using Eq.1 again, we get:

{

$$\varepsilon(n) - 2\varepsilon(n-1) + (1 + 2\pi\Delta T k)\varepsilon(n-2) = r(n) - 2r(n-1) + r(n-2)$$

(4)

This is a second order difference equation in  $\epsilon$  and the homogeneous solution is:

$$\varepsilon(n) = C_1(x_1)^n + C_2(x_2)^n$$

(5)

where

ĺ

$$r = 1 + i \sqrt{2\pi AT k}$$

(6)

and  $C_1 C_2$  are initial condition dependent constants. From the above we see that the system is unstable. The absolute value of x is always greater than unity for k > 0 and the error has exponential growth.

This is not surprising as both the accumulator and the DDS act as ideal integrator and the error signal is phase shifted 180 degrees by the double integration. The negative feedback thus turns into positive feedback!

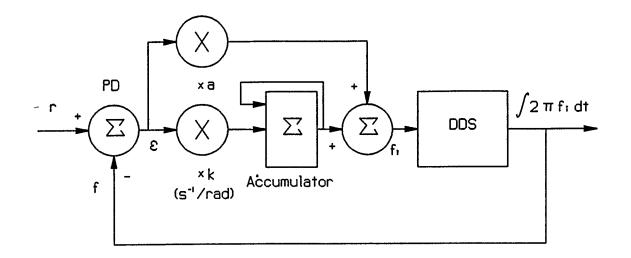

To achieve stability we let part of the error signals control the DDS directly as shown in Fig.2. The difference equation of the DDS output is now:

$$f(n) = f(n-1) + 2\pi \Delta T \left[ A(n-1) + \alpha \varepsilon(n-1) \right]$$

(7)

where  $\alpha$  is the fraction of error that directly controls the frequency of the DDS.

Fig.2A digital PLL block diagram with improved stability.

The error difference equation is now:

Í

ĺ

$$\varepsilon(n) - 2(1 - \pi \Delta T \alpha) \varepsilon(n-1) + [1 + 2\pi \Delta T(k-\alpha)] \varepsilon(n-2) = r(n) - 2r(n-1) + r(n-2)$$

(8)

The solution to the characteristic equation is:

.

$$x = (1 - \pi \Delta T \alpha) \pm \sqrt{(\pi \Delta T \alpha)^2 - 2\pi \Delta T k}$$

(9)

For real solutions it can be shown that for

$$0 < \alpha < \frac{1}{\pi \Delta T}, \quad k < \frac{\pi \Delta T \alpha^2}{2}$$

(10)

this system is stable. If we include complex solutions the condition of stability can be further relaxed.

An important consideration for accelerator application is the PLL's tracking

٠

capability with a changing reference. To examine this we rewrite the RHS of Eq.8 as follows:

$$r(n) - 2r(n-1) + r(n-2) = [r(n) - r(n-1)] - [r(n-1) - r(n-2)]$$

(11)

Divide Eq.8. by  $\Delta T$  the RHS now becomes:

( '

$$\frac{\Delta \phi_r(n)}{\Delta T} - \frac{\Delta \phi_r(n-1)}{\Delta T} = \omega_r(n) - \omega_r(n-1)$$

(12)

where  $\phi_r$  and  $\omega_r$  are the phase and frequency of the reference signal.

This is an important result. It shows that if the reference rf frequency ramps linearly, Eq.12 will be a constant and thus the RHS of Eq.8 will be constant. It is not difficult to see that a constant special solution for Eq.8 exists for the error function. Since the special solution is the steady state response of the system, we have just shown that the PLL is able to follow a linear frequency ramp of reference signal with a fixed phase error.