BNL-105818-2014-TECH EP&S No. 103;BNL-105818-2014-IR

## 16-Channel timing card with Q-BUS interface

G. Benenson

July 1983

Collider Accelerator Department

Brookhaven National Laboratory

#### **U.S. Department of Energy**

USDOE Office of Science (SC)

Notice: This technical note has been authored by employees of Brookhaven Science Associates, LLC under Contract No.DE-AC02-76CH00016 with the U.S. Department of Energy. The publisher by accepting the technical note for publication acknowledges that the United States Government retains a non-exclusive, paid-up, irrevocable, world-wide license to publish or reproduce the published form of this technical note, or allow others to do so, for United States Government purposes.

#### **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or any third party's use or the results of such use of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof or its contractors or subcontractors. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

Accelerator Department

BROOKHAVEN NATIONAL LABORATORY

Associated Universities, Inc.

Upton, New York 11973

EP&S Division Technical Note No. 103

G. Benenson July 28, 1983

#### 16-CHANNEL TIMING CARD WITH Q-BUS INTERFACE

#### I. General Description

Real-time monitoring/control systems often require that complex timing sequences be generated under micro-computer control. Standard "Pre-Det" or "Auto-Det" modules are not designed for direct computer interface; standard real-time clock/counter interface cards, such as DEC KWV11-A, are not designed to supply the multiple outputs required for complex control functions. As a result, timing problems are often "solved" through some uneasy combination of cumbersome interfacing; proliferation of modules, crates and cable; and compromise with the original requirements.

A need therefore exists for a multiple-output timing card which can be operated directly under computer control. This note describes such a module, which has been designed and tested for use in the Ionization Profile Monitor (IPM) System in the AGS main ring. The card is fully programmable from any LSI-11 microcomputer, and occupies one quad-height Q-BUS slot. A single 50-conductor flat cable handles all external communications. (See Table III).

#### II. User's Guide

#### A. Real-Time Control of Timing Sequences

The Q-BUS timing card is designed to supply 16 independent timing signals to external devices. There is no restriction on the interrelationship of these signals: they may be nonoverlapping, or partially or wholly overlapping. All outputs are normally synchronized to an external clock, which is accepted by the card as an input, via flat cable (Table III). A software "clock" may substitute for the real-time clock; the INCR and MAINT bits in the control/status registers (CSR) are used for this purpose. (See Table II.)

The incoming clock is used to increment the data counter register (DCR), which therefore contains a record of the current "time". THE MAXIMUM CLOCK FREQUENCY IS LIMITED TO 100 KHz; PULSE WIDTH MUST EXCEED 200 ns. The limitation on clock frequency makes possible the following trade-off: ANY REGISTER OR MEMORY LOCATION MAY BE ACCESSED AT ANY TIME; THERE IS NO CONFLICT WITH AN ONGOING TIMING SEQUENCE.

A timing sequence may be triggered in either of two ways, depending on the state of the MODE bit (Table II). In MODE 1, the external RESET line, also a flat cable input (Table III), automatically starts a sequence. In MODE 0, startup is under processor control. Receipt of a RESET causes the CSR ATTN bit to be set, and will also cause an INTERRUPT if the proper INTR ENABLE bits are "on" (Table II). In order to start a sequence, the processor must respond by writing to GO in the CSR. In either mode, the beginning of a sequence is signaled by an internal START pulse, and by reset of the CSR READY bit (Table II).

At the end of a sequence, the READY bit is automatically raised, indicating that the card may once again receive START. An INTER-RUPT may be programmed to occur at this time. Should a START occur (via GO or RESET) in the absence of READY, there would be an attempt to begin a new sequence before the previous one had terminated. In this case, an ERROR bit is set in the CSR, and an INTERRUPT may also be enabled (see Table II). Overflow of the data counter is also indicated by ERROR.

#### B. How Sequences are Programmed

Programming of the timing card is achieved using a 2K x 16 bit on-board memory, with full accessibility to Q-BUS; and by two special purpose registers: The address counter register (ACR) and the word counter register (WCR). The memory is organized into two parts: the lower half stores TIME data, which determines the "time" (i.e., data count) at which output pulses will occur; the upper half contains MASK DATA, which specifies the distribution of output pulses among the sixteen lines. These two pages of memory are geared together: each word in time data memory has its corresponding word at the same ll-bit address in MASK DATA memory. (Table I). Therefore, IK locations are available for combined time/mask data.

The large amount of available memory makes it possible to segment the memory into a number of discrete programs, each occupying a block of time/mask space. A program is then specified by two numbers: starting address and number of memory words. These two quantities are programmed by writing to the address counter register (ACR) and word counter register (WCR), respectively. Figure 1 shows the relationship between a sample program and the resulting timing sequence. Note that the ACR contains the first WORD address, i.e., the Q-BUS byte address

shifted right one position; and the word count is always expressed in two's complement representation. Both ACR and WCR actually consist of latch-counter/register combinations. At the beginning of a sequence, the counter is loaded from the latch; however, reading from Q-BUS gives the current countents of the counter (hence, the designation "counter/register"). Therefore, the ACR and WCR need not be pre-loaded before each sequence, but only when it is desired to switch to another program in time/mask memory.

From Fig. 1, it is apparent that each bit of mask memory corresponds to an output line. At any particular time, none, any or all the output lines may be activated. An active line will remain high until the "time" changes, i.e., until the next clock edge, unless the same output line is programmed "on" during the very next time data slot. Such is the case in Fig. 1 for output "O" and "7" during "5" and "6" data counts.

Two of the output lines, "O" and "1", may be programmed to produce INTERRUPTS as well as output pulses. The PROGRAM INTERRUPT ENABLE bits in the CSR are used for this purpose (Table II).

NOTE: All time data words within a program <u>must</u> be in ascending order; otherwise the logic will "hunt" for a "next" data word which has already been passed by the DCR, resulting ultimately in an ERROR flag.

#### III. Circuit Description

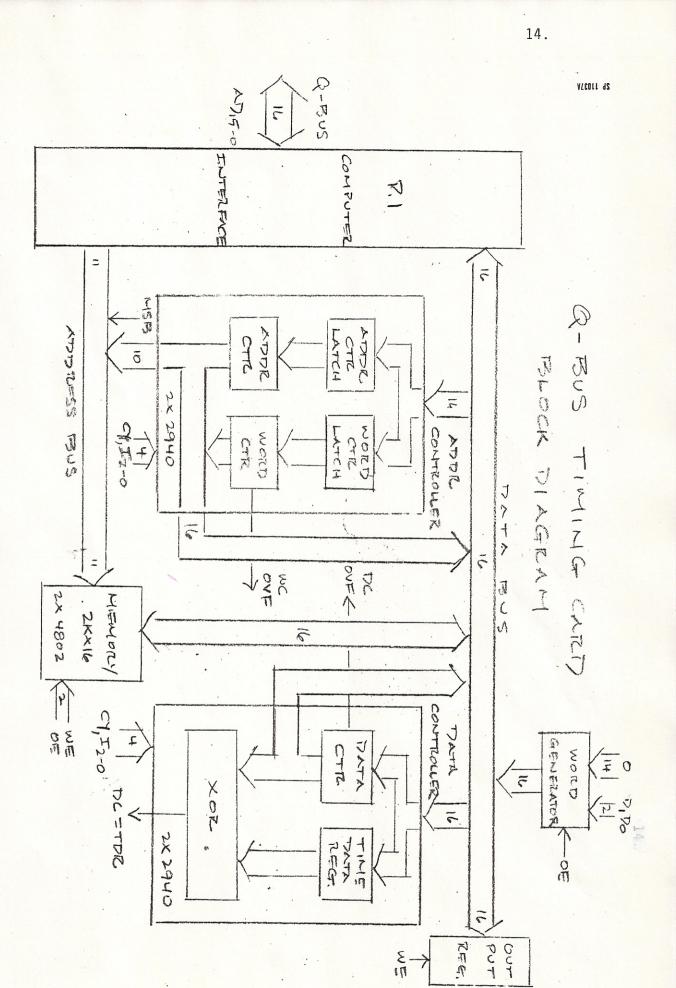

Schematics for the timing card are filed as Drawing D09-E1497-3, 1, 2 and 3 of 3. These will be referred to as P.1, P.2 and P.3, respectively. The block diagram attached as Fig. 3 indicates the relationship between the three pages. the COMPUTER INTERFACE (P.1) is concerned with driving and receiving Q-BUS, decoding register and memory addresses, and handling data transfer protocols and interrupt transactions. Data and address information are separated and applied to two bi-directional busses, which connect to the register and memory devices shown on P.3. Control logic is shown on P.2.

#### A. COMPUTER INTERFACE (P.1)

The connection to Q-BUS relies mainly on DEC DCK11 CHIPKIT interface devices.  $^1$  3A, 4A, 5A and 6A are DC005 bus transceivers, used to drive and receive Q-BUS data, and to detect addresses from the register bank (Table I). Memory bank addresses are detected by the address comparator 6B. Because of address/data multiplexing on Q-BUS, address information must be stored at BSYNCH time; this is done for register and memory addresses at 3C-2 and 1F-5, respectively. These signals are OR'ed

and gated with BSYCNH to form BUS REQUEST, 1C-8, which is an input to control logic, P-2.

The low-order 11 address bits (not including byte address, bit 0) are stored and driven on the ADDRESS BUS by register chips 3C and 5C; these form the local memory address for reading and writing to Q-BUS.

DEC interface chip DC003 (location 2A) handles the interrupt protocol; its inputs are the interrupt request and enable lines from the control section. Data transfer protocol lines BSYNCH, BRPLY, BDIN and  $BD0UT^2$  are buffered by transceiver chip lA; the DEC protocol chip DC004 was avoided because of its complexity and inflexibility.

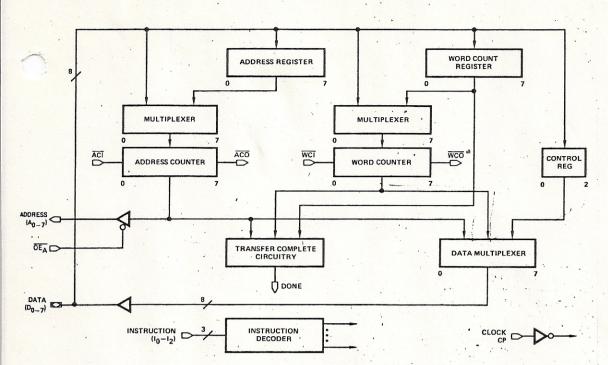

#### B. Memory/Register Section, P.3

The block diagram shown as Fig. 2 contains the elements of the memory/register section. The memory itself is made up of two Mostek MK4802-1 2K x 8 devices, chips 4B and 8B. These devices are configured as a 2K x 16 bit memory, and connected directly to the address and data busses. The two control lines, write enable (WE) and output enable (OE) are inputs from the control logic section, P.2. (OE gates memory data onto the tri-state data bus.).

The entire address counter register (ACR), word counter register (WCR) and their respective latches are contained within 2 Am2940 bitslice DMA controller chips (Fig. 3).<sup>3</sup> 10-bit addresses are produced by the address counter; the low-order 8-bits are handled by 4D; and the high-order 2 bits, byte 8D. The 6 high-order bits of 8D are not used. The 11th address bit, which selects TIME or MASK DATA page, is produced by the control logic section during real-time sequencing.

4D and 8D are labelled "address controller" on Fig. 2. They are operated in control Mode 3; i.e., both ACR and WCR are incremented together; and word count overflow (WCO) is brought out to indicate completion of a sequence. Control of this device is exercised by a carry (CY) input (used to inhibit counting), three instruction lines  $I_{2-0}$ , and an OE line which gates the ACR onto the tri-state address bus.

Another pair of 2940's 4E and 8E, are used to implement the data counter register DCR; the time data register (TDR), used to store the time data word from memory at which the next pulse outputs will occur; and the comparator, which compares the two. These two chips are labelled DATA CONTROLLER on Fig. 2. The 2940 address counter is used as the DCR; the word counter is used as TDR; and the devices are operated in Mode 2, so that the TDR is never incremented, and the comparator output is brought out via the DONE pin.<sup>3</sup> Outputs are therefore COMPARE

(i.e., DONE, or DCR=TDR) and data counter overflow (DCO). Inputs from the control logic section are instruction bits  $I_{2-0}$  and CY. The address bus connection is not used.

Note that three of the four bus accesssed registers, WCR, ACR and DCR, are physically located within controller chips. The connection to Q-BUS for both reading and writing is made via the bi-directional data bus; and control during bus operations is exercised via the instruction bits.

Figure 2 shows two other devices attached to the data bus: these are the word generator (WG) 3H and 8H; and the output register (OR) 4H, 5H, 6H and 7H. WG is used to load constants onto the data bus; its operations include clearing the OR and DCR, and loading mode numbers into the control registers of all four controller ships. OE and 2 data bits are supplied by control logic. The output register is loaded from the mask data memory to produce the programmed pulse outputs, and cleared from WG between pulses. The WRITE ENABLE (WE) line is an input from control logic.

#### C. Control Logic Section, P.2

As the foregoing description suggests, there are two independent sources of control for the memory and controller devices on the timing card. Commands may be asserted by the processor, via Q-BUS; or they may be caused by real-time events entering the timing card as CLOCK and RESET. Existence of two independent sources poses two fundamental problems for the internal control logic. The two pathways must be SYN-CHRONIZED (i.e., prevented from conflicting with one another) and MULTI-PLEXED (i.e., a choice must be made between them in determining the active source at any particular time).

The two control pathways are shown entering the control logic schematic (P.2) from the left and right, as BUS RQST/WRITE RQST and EXT CLOCK/EXT RESET, respectively. These inputs are synchronized to a common 10 MHz master clock (MCK) which originates from oscillator 7E (P.3). Synchronization of bus and real-time inputs is performed by registers 2D and 10H, respectively. Gates 1D-3 and 10F-6 prevent more than one control pathway from being active during a MCK cycle; and use of the NOR connection at 1E-5 awards priority to the bus pathway in case of a tie.

The major outputs of the control logic section are the inputs to memory/register (P.3) discussed above. Most of these lines are produced by 3 32-bit PROM chips, 9B, 9C and 9D, with output buffer register 10B and 10C. PROM 9B is enabled by the BUS REQUEST pathway; 9C and 9D are enabled by real-time requests via JK flip-flops 10D and 9F. As discussed above, the two enables are mutually exclusive. The PROM chips are open-collector devices with pull-ups supplied by resistor pack 9A.

Unless enabled, all PROM outputs are high; however, control outputs are low-true. Six of the output lines, including memory OE and five controller I lines, may be driven from either the bus or the real-time pathway. These lines are therefore derived from the wire-OR of 9B and 9C, made possible by low-true outputs and mutually exclusive enables.

Table IV shows the program for 9B. The enable pin 9B-15 is derived from 2D-12, the BUS REQUEST line after synchronization of the five address lines. One address bit selects READ or WRITE; another selects memory or register access; and two select the particular register (Q-BUS address bits 2 and 1). The remaining line, DEL, is the ENABLE bit delayed one clock cycle. This bit is used to limit memory WE to one clock cycle in width.

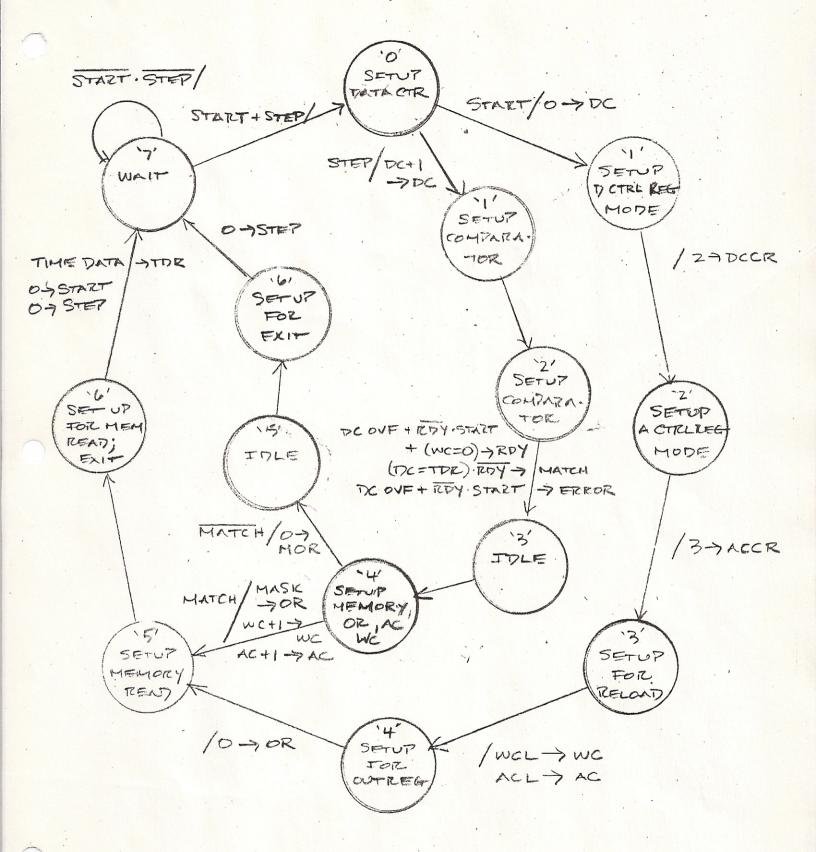

Table V shows the program for PROMS C and D, concerned with real-time control. These PROMS implement the state table shown in Fig. 4. Inputs CLOCK and RESET are synchronized at 10H-15 and 10H10, respectively. The additional delay at 9H-7 and 9H-2 is used to develop a leading edge detector, 6D-8 and 6D-6, which generates a pulse 100 ns wide regardless of the original width of CLOCK and RESET respectively (except that they must exceed 200 ns, minimum). Note that MODE is a condition on RESET; and MAINT is a condition on CLOCK. These bits are brought in from the CSR (see below). Also note that GO may substitute for RESET; and INCR may substitute for CLOCK. These CSR write-only bits, already synchronized to MCK by the bus control pathway, are ORed into the CLOCK and RESET pathways at 6C-6 and 6C-3. The real-time requests are then stored by JK flip-flop 10D as STEP and START respectively. These lines are ORed, delayed one clock cycle to detect a conflict with the bus control pathway, and then used to form the enable bit for PROMS 9C and 9D.

Three of the five address bits for 9C and 9D are "next state" bits which represent an increment of the current state. The control state counter is implemented within 9D itself. The resting state is "7" due to the use of active low logic. Figure 4 shows an outer loop which is selected by START and an inner loop which executes a STEP. The choice is made in the PROMS by address bit 4. The remaining PROM address bit distinguishes between match and non-match conditions within the data controller, i.e., between DCR=TDR and DCR≠TDR. This bit is used to branch within the inner loop. Note that all outputs of the PROM, including "next state" information, are deskewed by 10B and 10C before taking effect. For example, set up of the DCR, which takes place during state "7" (once the ENABLE is present) will produce control bits for the word generator and/or data controller. These bits will be loaded into the register along with the "next state" information. As set-up lines, they will be observed by the memory or register device(s) only on the NEXT edge of MCK. Thus, there is a two cycle delay between the state

information presented to the address port of PROM and the resulting register change of state.

P.2 also includes the CSR. 6F contains the STATUS bits, clocked upon leading edge detection of RESET, 6C-8. The ATTN bit is set simultaneously, provided MODE is low. This transition is set up at 9F-3 and appears at 9F-5 from which point it is gated onto the data bus via 7F-15. Any transition of the READY bit is enabled during state "2". NOTE THAT THE RAISING OF READY AT THE END OF A SEQUENCE REQUIRES ONE ADDITIONAL CLOCK BEYOND THE LAST TIME DATA WORD IN THE PROGRAM. MATCH (i.e., DCR=TDR) and ERROR are likewise clocked during state "2" and these also appear as outputs of 9E.

INTERRUPT, ENABLE, MAINT and MODE bits are stored in 3F and 5F and the INCR and GO bits are brought in via 6E-6 and 6E-12, respectively. READY, ATTN and ERROR interrupt requests are developed by gates 1H and 2C; as are program interrupts which are triggered by pulse outputs 1 and 0, and stored by flip-flop 2H.

#### References

- 1. "DCK-11-AA Program Transfer Interface," in <u>Microcomputer Interface</u> Handbook, Pp. 114-133, Digital Equipment Corp., 1980.

- 2. "LSI-11 Bus," in <u>Microcomputers and Memories</u>, Ch. 9, Digital Equipment Corp., 1982, see especially "Data Transfer Bus Cycles," pp. 223-233.

- 3. "Am2940," Bipolar microprocessor Logic and Interface Data Book, pp. 6-307--6-315, Advanced Micro Devices, 1981.

#### REGISTER FORMAT

| 人ワワルにちち   | DIESCRIPTION            | CONTENT                              |

|-----------|-------------------------|--------------------------------------|

| 7571×××0  | WOILD COUNTER REGISTER  | MEMORY WORD COUNT (TWO'S COMPLEMENT) |

| 757 xxx 2 | ADDR COUNTER REGISTER   | MEMORY STARTING                      |

| 7{7}xxx4  | CONTROL STATUS REGISTER | SEE TABLE 2                          |

| 7{7}xxx6  | DATA COUNTER REGISTER   | CURRENT TIME                         |

### MEMORY FORMAT.

|           | ADDIESS | DISCUPTION       | CONTENT               |

|-----------|---------|------------------|-----------------------|

|           | XX 0000 | TIME DATA MEMORY | TIME VALUES AT WHICH  |

|           | · ·     |                  | OUTPUT PULSES OCCUR   |

|           | XX3777  |                  | (ASCIENTING SEQUENCE) |

|           | XX 4000 | MASK DATA MEMORY | OUTPUT PATTERN OF     |

| 100       | •       |                  | PULSES FOR EACH TIME  |

| Section . | XX7777  |                  | DATA POINT            |

SELECT SWITCHES NOTE: OPEN = 0; CLOSED = 1 BIT LOCATION 17/16/15/14/13/12/11/10/9/8/7/6/5/4/3/2/11/0 DEVICE ASSIENMENT SWITCH SELECT REGISTER SWITCH LOC. 70 BANK SWITCH I 8765432 SW. SELECT \*\* LOCAL MEMORY ADDRO ASSIENMENT MEMORY 78 SWITCH BANK 654321 SWITCH 000000000 SW, SELECT \*\*\* 00 ASSIGNMENT INTERRUPT TA SWITCH VECTOR SWITCH 654321

SP 11037A

\* PRICE SELECT (SEE REGISTER FORMAT)

\*\* PAGE SELECT (TIME DATA = 0; MASK DATA = 1)

\*\* CHANNEL SELECT (A=0; B=1)

TABLEI

# Q-BUS TIMING CARD CONTROL/STATUS REGISTER

| 15     | 14   | 13 | 12  | 11 | 10      | 9      | 8       | 7      | 6  | 5  | 4   | 3  | 2   | 1   | 0   |

|--------|------|----|-----|----|---------|--------|---------|--------|----|----|-----|----|-----|-----|-----|

| -20    |      | 5- | TAT | U5 | Tue     | MAINT  | MODE    | 200    | IN | ナー | てない | PT | ENA | BLE | GO  |

| 1 - WK | HITA | 2  | }   | 0  | IT WE'V | 1-(10) | , tolle | icer [ |    |    |     |    | PSM |     | 1 1 |

| BIT             | 1      | AME          | TYPE          | DESCRIPTION                                                                                                                           |

|-----------------|--------|--------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Ġ               | Go     |              | WRITE         | SETS START; REQUIRED TO INITIATE TIMING                                                                                               |

| ı               | H 2    | PROGRAM      | R/W           | ENABLE INTERRUPT CHANNEL A. ON PULSE OUTO                                                                                             |

| 2               | TER    | PROGRAM<br>B | 12/W          | " " B" " OUT,                                                                                                                         |

| 3               | 2      | ATTN         | R/W           | 1 A 1 ATTH BIT                                                                                                                        |

| 4               | P -    | READY        | R/W           | B" READY"                                                                                                                             |

| 5               | ENG    | FREOR        | 72/W          | " B" FRROZ!                                                                                                                           |

| L               | BLE    | MASTER       | R/W           | MUST BE SET FOR ANY INTERBUPTS TO OCCUR                                                                                               |

| 7               | 721    | EATTY        | <b>ルミ人</b> !フ | THRICATES TIMING SEQUENCE NOT IN PROCRESS  SET BY WORD COUNTER OVERFLOW OF ERROR  RESET BY STATTIREADY OR INIT                        |

| ٤               | M      | ODE          | R/W           | SELECT CONDITION FOR START: MODE =0-> MODE =1-> AUTO START ON EXT RESET USEGO TO START                                                |

| 9               | Μ,     | NINT         | R/W           | DISABLE EXTERNAL CLOCK; MAINT = 1 ->  INCR BIT MUST BE USED TO STEP DATA CTR                                                          |

| 10              | 工      | JCR          | WZITE         | SOFTWARE INCREMENT OF TATA COUNTER;                                                                                                   |

| 11              | 5      | O            | ルミヘブ          | STATE OF 3 EXTERNAL STATUS LINES                                                                                                      |

| 12              | A<br>T | •            | THAT          | SAMPLED AT EXT. RESET TIME                                                                                                            |

| 13              | 5      | 2            | READ          |                                                                                                                                       |

| 14              | 八      | 7            | READ          | INTICATES EXT RESET RECEIVED IN MODE O; WAITING FOR GO SET BY EXT RESET MODE; RESET BY GO + INIT                                      |

| 15<br>SP 11037A | E      | ror          | ZEAT)         | JUDICATES FAILURE TO EXIT FROM TIMING-<br>SEQUENCE, SET BY DATA COUNTER OVERLIOW<br>OR START. READY, RESET BY START. READY<br>OR INIT |

## CABLE FORMAT

|   | - 1            |                                            |

|---|----------------|--------------------------------------------|

|   | <u>_</u>       |                                            |

|   |                |                                            |

|   |                |                                            |

|   | 101.1          |                                            |

|   | 5 -            | PULSE OUTO                                 |

|   | 37             | 1                                          |

|   | 2 w            | 2                                          |

|   | 1              |                                            |

|   | 5 12           | 3                                          |

| • |                | 4 /                                        |

|   | 2 0 0          | 5                                          |

|   | 7 ~            | 6                                          |

|   |                |                                            |

|   | 1-1            | 7 TO EXTERNAL                              |

|   | 3 2            | 2 DEVICE                                   |

|   | 7 2            | 9 -                                        |

|   | 9 =            |                                            |

|   |                | 10                                         |

|   | 36.39          | II a la l |

|   | 3 5            | 12                                         |

|   | 은 =            | 13                                         |

| _ | 36.            |                                            |

| h | 10 -           | 14/                                        |

|   | 2 3            | 15                                         |

|   | 34             | STATUS 2                                   |

|   | 50             |                                            |

|   | 32,33          | Trans arch                                 |

|   |                | FROM AGS/TTL                               |

|   | 2 3            | EXT CLOCK LEVEL SHIETER                    |

|   | 23 22 21       | EXT RESET                                  |

|   | 22             |                                            |

|   | 23 23          |                                            |

|   |                |                                            |

|   | 12 22<br>15 24 |                                            |

|   | 22 22          |                                            |

|   | 1              |                                            |

|   |                |                                            |

|   | ᆜ              |                                            |

|   | _              |                                            |

|   |                |                                            |

TABLE III

Q-BUS FILITA CARD. BUS CONTROL PROY

|   |        |        |     |    | 2        |   |          |            |    |        | mare    |       | <   |     |     | かだける   |            |          | ワテムラ   |      | 4      |        |         | REAT      |    |      | ときなり   |   |          |        | _        | REAT |                                         |

|---|--------|--------|-----|----|----------|---|----------|------------|----|--------|---------|-------|-----|-----|-----|--------|------------|----------|--------|------|--------|--------|---------|-----------|----|------|--------|---|----------|--------|----------|------|-----------------------------------------|

|   |        |        |     |    | 707      |   |          |            |    |        | エロこ     |       | 20  | 253 | かった | WC iZ  |            |          | I<br>I |      | 700    | 250    | ACE     | mcr       |    |      | 2      |   | nc       | 250    | かつだ      | mcz. |                                         |

|   | U      | 4      | 29  | 25 | 77       | R | 25       | 27         | 23 | 22     | Ŋ       | 20    | 2   |     | シ   | 5      | <u>√</u> 1 | <u>.</u> | ū      | 17   | =      | 5      | 2       | 00        | 7  | 6    | N      | ٦ | N        | N      | -        | 0    |                                         |

|   | _      | -      | _   | _  | <u> </u> | _ |          |            | _  | _      | <br>-   |       |     | _   | _   |        |            |          |        |      |        |        |         |           |    |      |        | C |          |        |          |      | A                                       |

|   | -      | _      | -   | _  | _        | _ | _        | _          | 0  | 0      | 0       | 0     | G   | 0   | 0   |        | _          | _        | _      | _    | -      | -      | -       | -         | 0  | c    | 0      | C | c        | 0      | 0        | 0    | i k                                     |

|   | ·<br>  | -      | -   | -  | 0        | 0 | 0        | 0          | _  | -      | -       | -     | 0   | C   | 0   | Ö      | -          | _        | _      | -    | 0      | 0      | 0       | 0         | -  | -    | -      | - | C        | 0      | 0        | 0    | 312                                     |

|   | -      | -      | 0   | 0  | -        | - | 0        | 0          | -  | _      | 0       | 0     | -   | -   | 0   | 0      | -          | -        | 0      | 0    | -      | -      | 0       | 0         | -  | _    | 0      | 0 | -        | -      | 0        | 0    | 25                                      |

|   | _      | c      | -   | С  | _        | 0 | -        | c          | -  | 0      | -       | 0     | _   | 0   | _   | O      | -          | 0        | -      | 0    | -      | 0      | -       | 0         | -  | 0    | -      | 0 | -        | 0      | -        | 0    | 250                                     |

|   |        |        |     |    |          | , |          |            |    |        |         |       |     |     |     |        | ,          |          |        |      |        |        |         |           |    |      |        |   |          |        |          |      | , ,                                     |

| i | -<br>n | -<br>m | 1.7 | 10 | _<br>D   | ī | ē        | <u>c</u> 9 | ī  | 11     | -<br>J1 | 7     | - 3 | - 2 | _   | 0      | 0          | о<br>П   | 00     | 0    | o<br>U | 0      | 0       | <b>C8</b> | 10 | 2    | 2      | t | 0        | n      | <u>a</u> | 0    | HEX YARAY                               |

|   |        |        |     |    |          |   |          |            |    | •      |         |       |     |     |     |        |            |          |        |      |        | 'n     |         |           |    |      |        |   |          |        |          |      |                                         |

|   |        |        | 7   | -  |          |   |          |            |    |        |         |       |     |     |     |        |            |          |        |      |        |        |         | * .       | ,  |      |        |   |          |        |          |      | 76-                                     |

|   |        |        |     |    |          |   |          |            |    |        |         |       | ı   |     |     |        |            |          |        |      |        |        |         |           |    |      |        |   |          |        |          |      |                                         |

|   | T      | TI     | T   | TI | TI       | Ħ | TI<br>TI | TI         | TI | n<br>n | TI TI   | T1    | n   | TI  | AA  | m<br>T | 71         | T        | U<br>U | コロ   | F7     | m<br>D | 17      | Dr.<br>TI | コー | コー   | Γ<br>π | 7 | 7        | T<br>U | II       | T    | JH AX                                   |

|   |        |        |     |    |          |   |          |            |    |        |         |       |     |     |     |        | '          |          |        |      | '      |        |         |           | •  |      |        |   |          |        |          |      |                                         |

|   |        |        |     |    |          |   |          |            |    |        |         |       |     |     |     |        |            |          |        |      |        |        |         |           |    |      |        |   |          |        |          |      |                                         |

|   |        |        |     |    |          |   |          |            |    |        |         |       | ,   |     |     |        |            |          |        |      |        |        |         |           |    |      |        | , |          |        |          |      |                                         |

|   |        |        |     | ,  |          |   |          |            |    |        | (       | _     | _   | _   | _   | _      | C          | 0        | 0      | 0    | _      | _      | -<br>-≠ | -         | C  | 0    | С      | 0 |          | _      | _        | _    | 0 0 1                                   |

|   |        |        |     |    |          |   |          |            |    |        | -       | -     | _   | _   | _   | _      | _          | _        | _      | _    | _      | _      |         | 0         | _  |      | _      | _ | _        | _      | 0        | 0    | 0 417                                   |

|   |        |        |     |    | !        | • |          |            |    |        |         | _     | _   | _   | 0   | _      | -          | _        | _      | _    | -      | _`     | _ '     | _         | _  |      |        | _ | _        | _      | _        | _    | 7 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 |

|   | ,      |        |     |    |          |   |          |            |    |        |         | -]-   |     | _   | - 1 | 0      | -          | _        |        | _    |        | _      |         | 0         |    |      |        | _ | _        | _      | _        | 0    | 25.5                                    |

|   | <      |        |     |    |          |   |          |            |    | ٧      | 1       | -  -  | -   | -   |     | -      |            | _        |        | - 0  | · ·    |        |         | -         |    | <br> |        | - | <u> </u> |        |          |      | 0 H/s                                   |

|   |        |        |     |    |          |   |          |            |    |        |         | - 0   | ) - |     |     | -      | _          | -        |        | _  - |        |        |         | .         |    |      | _      | - | -        | _      |          | -    | 0 4 g                                   |

|   |        |        |     |    |          |   | 3        |            |    |        | 1-      | -  -  | -   |     |     |        |            |          |        | -  - | - (    | , -    |         | .  -      |    |      |        | - | - (      | ,      |          | -    | 23 310                                  |

|   |        |        |     |    |          |   |          |            |    |        | (-      | -   - | . 0 | ) - | -   | .      | -          |          |        | -  - | -      |        |         | -  -      |    |      |        | - |          | -      |          | •    | -0 #1 P                                 |

TABLETY

Q-BUS TIMING CARD - REAL-TIME CONTROL PROY

|   |         | 7/10,010 |        | 'L'-1' | てルインドウス | 15 TSB=0 | LOT OF       | 101111 んんん | 452=0  | ジーナ のしの   |          | 12'-7'3' ZESTA AC |        | 11 12 3 ALACA |     | '0'1' 21 DCR |        | アイング ゴーハマ かん |    | 1.5.7    | 5-16 HEM - TOR. | 1  | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 100 | HOLL MENTON THEN AC | NOT B TON |   | 12/13/ |          | ハイング・ |   | 041     |      | 0 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 |         |

|---|---------|----------|--------|--------|---------|----------|--------------|------------|--------|-----------|----------|-------------------|--------|---------------|-----|--------------|--------|--------------|----|----------|-----------------|----|---------------------------------------|-----|---------------------|-----------|---|--------|----------|-------|---|---------|------|-----------------------------------------|---------|

|   | -       | -        | . —    | -      | _       | -        | _            | _          | _      | -         | _        |                   | _      | -             | -   | _            | 0      | 0            | 0  | 0        | 0               | C  | 0                                     | 0   | 0                   | 0         | 0 | 0      | 0        | G     | O | С       | 7.   | Small                                   |         |

|   | -       | -        | -      | -      | -       | -        | -            | _          | C      | 0         | 0        | 0                 | 0      | С             | 0   | 0            | -      | -            | -  | -        | -               | -  | -                                     | -   | 0                   | c         | 0 | 0      | 0        | C     | 0 | 0       | 2    |                                         |         |

|   | -       | -        | -      | -      | c       | С        | С            | O          | -      | -         | -        | -                 | О      | c             | 0   | C            | -      | -            | _  | -        | C               | 0  | 0                                     | 0   | -                   | _         | - | -      | 0        | 0     | С | О       | 17   | שרי דו                                  |         |

|   | -       | -        | C      | C      | -       | -        | 0            | G          | -      | -         | С        | C                 | -      | -             | c   | 0            | :<br>_ | -            | 0  | 0        | -               | -  | 0                                     | 0   | -                   | -         | 0 | 0      | _        | -     | 0 | 0       | >    | c                                       |         |

|   | L       | C        | -      | 0      | -       | C        | -            | 0          | -      | О         | -        | С                 | -      | c             | -   | C            | -      | С            | -  | 0        | _               | 0  | -                                     | 0   | -                   | o         | - | 0      | -        | 0     | - | 0       | 8    | HARRI LIST                              |         |

| 1 | -<br>TI | -<br>m   | _<br>U | 0      | ۔<br>تر | -<br>>   | - 0          | 60         | 17     | - 0       | -<br>-   | ŧ<br>-            | ر<br>د | - 2           |     | 0            |        | 0<br>111     |    |          |                 | 0  |                                       |     | 01                  |           |   | t      |          | 0     |   | 0       | ふつかる | E A                                     |         |

|   |         | 11       | 1      |        | コロ      | ココ       | 77           | T<br>n     | U C    | TI        |          | Ω<br>Π            |        | 411.7         | F 2 | T P          |        | η<br>η       |    | TI<br>TI | 7 11            | пп | 7 =                                   | ПП  | コレ                  | ココ        |   |        | TI<br>TI |       | π | T T     | DATE | T A                                     |         |

|   | -       | -        | -      | -      | g       | C        | 0            | 0          | -      | -         | -        | -                 | -      | -             | -   | -            | -      | -            | _  | -        | 0               | -  | 0                                     | -   | 0                   | -         | - | -      | -        | -     | - | -       | 0    | 17 10                                   |         |

|   | _       | _        | -      | -      | -       | _        | -            | _          | -      | -         | -        | -                 | 0      | 0             | -   | -            | -      | -            | -  | -        | -               | -  | _'                                    | -   | -                   | -         | - | -      | -        | -     | - | -       | 3    | 7                                       |         |

|   | -       | -        | -      | -      | -       | 1 ,      | -            | -          | -      | -         | 0        | 0                 | 0      | 0             | -   | -            | -      | -            | -  | -        | -               | -  | 100                                   | 1.4 | -                   | -         | - | -      | -        | -     | - | -       | o    | 74 4                                    | PRO     |

|   | _       | -        | -      | ,      | -       | -        | -            | -          | -      | -         | C        | 0                 | 0      | 0             | _   | -            | -      | -            | -  | -        | -               | -  | •                                     | 1   | -                   | -         | 2 | -      | -        | -     | 1 | -       | 9    | भन्ने                                   | 2019    |

|   | -       | -        | -      | 1      | -       | -        | -            | -          | -      | -         | -        | -                 | -      | -             | 0   | 0            | -      | -            | -  | -        | -               | -  | -                                     | -   | -                   | -         | - | -      | -        | -     | - | -       | 0    | T'E                                     | 0       |

|   | 0       | 0        | -      | -      | -       | -        | -            | -          | -      | -         | -        | -                 | -      | -             | 0   | 0            | -      | -            | -  | -        | -               | -  | 1                                     | -   | -                   | -         | - | -      | -        | -     | - | -       | 8    | H 3                                     |         |

|   | 0       | 0        | -      | -      | -       | -        | -            | -          | 0      | 0         | 1        | -                 |        | -             | -   | -            | -      | -            | -  | -        | -               | -  | -                                     | -   | -                   | 0         | - | -      | -        | -     | - | - (     | 0,   | 71 %                                    |         |

|   | 0       | 0        | -      | -      | -       | -        | -            | _          | G      | 0         | _        | -                 | _      | -             | 0   | G            | -      | -            | -  | -        | -               | -  | -                                     | -   | -                   | 0         | - | -      | _        | -     | _ |         | 0    | 3 &                                     |         |

|   |         |          | =      |        |         | =        | <del>-</del> |            | 7      | 7         | <u> </u> | η                 | T      | TI            | .7  | J            | Ti     | Ш            | TI | n        | 7               | п  | 7                                     | П   | U                   | ח         | η | n      | Π.       | π     | Π | <u></u> | DA   | I<br>M                                  |         |

|   | η<br>0  |          |        | TI     | カカ      | T T      | 7            |            | t<br>7 | 0.1 -1.29 | n        | な                 |        |               | -   | -            | a      | 00           |    |          |                 |    |                                       | י ס |                     | ŧ         | J | J      |          |       | 9 | ۵.      | ATA  | ۲                                       |         |

|   | -       | -        | -      | -      | c       | 0        | 0            | 0,         | 0      | 0         | -        | -                 | -      | -             | -   | -            | -      | -            | -  | -        | 0               | -  | 0                                     | -   | -                   | -         | - | -      | -        | -     | - | -       | 0    | 1 2 7                                   |         |

|   | -       | -        | -      | -      | -       | -        | -            | -          | -      | -         | -        | _                 | -      | -             | -   | -            | -      | -            | -  | -        | -               | -  | -                                     | -   | 0                   | -         | - | -      | -        | -     | - | -       | 3    | 512                                     |         |

|   | -       | -        | -      | -      | 0       | 0        | -            | -          | -      | -         | -        | -                 | -      | -             | 0   | 0            | -      |              | -  | -        | 0               | -  | -                                     | -   | -                   | -         | - | -      | -        | -     | - | -       | 06   | 43                                      | PRO     |

|   | -       | _        | _      | -      | -       | -        | -            | -          | -      | -         | _        | -                 | -      | _             | -   | -            | 0      | C            | -  | -        | -               | -  | -<br> -                               | -   | -                   | -         | _ | -      | -        | -     | - | -       | 20   | 513                                     | PROM 9D |

|   | 0       | 0        | -      | -      | -       | -        | -            | -          | 3      | 0         | -        | -                 | 0      | 0             | 0   | 0            | -      | -            | -  | -        | -               | -  | -                                     | -   | -                   | 0         | - | -      | -        | -     | - |         | 0    | Call                                    | J       |

|   | 0       | 0        | -      |        | -       | -        | -            | -          | -      |           | 0        | 0                 | 0      | 0             | 0   | 0            | 0      | 0            | -  | -        | -               | -  | -                                     | -   | -                   | -         | 0 | 0      | 0        | 0     | 0 | 0       | 20   | 1 4                                     |         |

| , | 0       | 0        | -      |        | -       | -        | 0            | 0          | C      | 0         | -        | -                 | -      | -             | G   |              | 1      | 0            | 1  | -        | -               | -  | C                                     | 0   | 0                   | 0         | - | -      | -        | -     | 0 | 0       | 3    | - 577                                   |         |

|   | 0       | 0        | 1-     | -      | 0       | 0        | 1-           |            | c      | 0         | -        | -                 | c      | 0             | -   | -            | 10     | 0            | -  | -        | 10              | 10 | <b> -</b>                             | -   | 0                   | 0         | - | -      | 0        | 0     | - | -       | P    | h o                                     |         |

TABLE X

| Q-BUS TIMING CARD - SAMPLE PROGRAM               |                  |

|--------------------------------------------------|------------------|

| ADDRESS TIME DATA ADDR MASK DATA (BIHARY)        | y                |

| (OCTAL) (OCTAL) (OCTAL) 15-876543210             | -                |

| XX2742 3 XX6742 5( 01100001                      | dependent vision |

| XX 27 44 5 XX 6744 (                             |                  |

| xx 27 46 6 xx 67.44 5 1 1000000 1 xx 2750 11 001 |                  |

|                                                  | ı                |

| THEGISTER 177774 ATTOR CHE 001361                |                  |

| = - 4 (OCTAL) = STARTING APPOR -2 (OCTAL)        |                  |

| RESULTING SEQUENCE                               |                  |

| STATET                                           |                  |

| ack TATATATA                                     |                  |

| DATA COUNTER X 0 1 2 3 4 5 6 7 10 11 12          |                  |

| WORD COUNTER 17774 17775 17776 17777 0.          |                  |

| NOTE COUNTER 1361 1362 1363 1364                 |                  |

| MEM, ADDINESS 2742/6742 2744/6744 2750/6750      |                  |

| [2746/6746]                                      |                  |

| READ!                                            | -                |

|                                                  |                  |

|                                                  | _                |

| ? !                                              |                  |

|                                                  |                  |

|                                                  |                  |

| E 3                                              | -                |

| 0 4                                              |                  |

| T 5:                                             | -                |

| V 6                                              |                  |

|                                                  |                  |

FIGURE 1

=

NOTES: 2, ITXCEPT FOR BUS INTERFACE (P.I)

DINGERAM ARE FOULD ON P. & 1, LABELLEY ARROWS CONTROL LOCIC SECTION P. 7 ヨントもし」 ARE CONTROL LIVES 7 RIGGES SHOWS ON THIS मिल्न निर नि

DMA

CONTROLLER

#### **Control Register**

CR<sub>2</sub> CR<sub>1</sub> CRo

|                 |                 | Control Mode | Control                | Word      | · DONE O                                     | tput Signal                              |  |  |

|-----------------|-----------------|--------------|------------------------|-----------|----------------------------------------------|------------------------------------------|--|--|

| CR <sub>1</sub> | CR <sub>0</sub> | Number       | Mode Type              | Counter   | WCI = LOW                                    | WCI = HIGH                               |  |  |

| L               | , L             | 0            | Word Count Equals Zero | Decrement | HIGH when<br>Word Counter = 1                | HIGH when<br>Word Counter = 0            |  |  |

| L               | Н               | 1            | Word Count Compare     | Increment | HIGH when Word Counter + 1 = Word Count Reg. | HIGH when Word Counter = Word Count Reg. |  |  |

| н               | L               | 2            | Address Compare        | Hold      | HIGH when Word Cour                          | nter = Address Counter                   |  |  |

| н               | Η,              | 3            | Word Counter Carry Out | Increment | Alwa                                         | - Always LOW                             |  |  |

H = HIGH L = LOW

| CR <sub>2</sub> | Address Counter |

|-----------------|-----------------|

| L               | Increment       |

| Н               | Decrement       |

#### **TABLE I. Am2940 INSTRUCTIONS**

| ٠<br>کا | 4 | 6 | Octal<br>Code | Function                     | Mnemonic | Control<br>Mode | Word<br>Reg. | Word Counter | Address<br>Reg. | Address<br>Counter | Control<br>Register                | Data<br>D <sub>0</sub> -D <sub>7</sub>        |

|---------|---|---|---------------|------------------------------|----------|-----------------|--------------|--------------|-----------------|--------------------|------------------------------------|-----------------------------------------------|

| L       | L | L | 0 -           | WRITE<br>CONTROL<br>REGISTER | WRCR     | 0, 1, 2, 3      | HOLD         | HOLD         | HOLD            | HOLD               | D <sub>0</sub> -D <sub>2</sub> →CR | INPUT-                                        |

| L       | L | н | 1             | READ<br>CONTROL<br>REGISTER  | RDCR     | 0, 1, 2, 3      | HOLD         | HOLD         | HOLD            | HOLD               | HOLD                               | CR→D <sub>0</sub> -D <sub>2</sub><br>(Note 1) |

| L       | н | L | 2             | , READ<br>WORD<br>COUNTER    | RDWC     | 0, 1, 2, 3      | HOLD         | HOLD         | HOLD            | HOLD               | HOLD                               | wc→b                                          |

| L       | н | н | 3             | READ<br>ADDRESS<br>COUNTER   | RDAC     | 0, 1, 2, 3      | HOLD         | HOLD         | HOLD            | HOLD               | HOLD                               | AC+D                                          |

| н       | ı | L | 4             | REINITIALIZE                 | REIN     | 0, 2, 3         | HOLD         | WCR→WC       | HOLD            | AR-+AC             | HOLD                               | Z                                             |

| -       | _ |   |               | COUNTERS                     | HEIN     | 1               | HOLD         | ZERO→WC      | HOLD            | AR-AC              | HOLD                               | Z                                             |

| н       | L | н | 5             | LOAD<br>ADDRESS              | LDAD     | 0, 1, 2, 3      | HOLD         | HOLD         | D→AR            | D→AC               | HOLD .                             | INPUT                                         |

| н       | н | 1 | 6             | LOAD<br>WORD                 | LDWC     | 0, 2, 3         | D→WR         | D→WC         | HOLD            | HOLD               | HOLD                               | INPUT                                         |

| -       | - | • | . 0           | COUNT                        | LDWC     | 1               | D→WR         | ZEROWC       | HOLD            | HOLD               | HOLD                               | INPUT                                         |

| н       | н | н | 7             | ENABLE                       | ENCT     | 0, 1, 3         | HOLD         | ENABLE COUNT | HOLD            | ENABLE<br>COUNT    | HOLD                               | z                                             |

|         |   |   |               | COUNTERS                     | ENCI     | 2               | HOLD         | HOLD         | HOLD            | ENABLE<br>COUNT    | HOLD .                             | Z '                                           |

CR = Control Reg.

AR = Address Reg.

AC = Address Counter

WCR = Word Count Reg. WC = Word Counter D = Data

L = LOW H = HIGH Z = High Impedance

Note 1: Data Bits D<sub>3</sub>-D<sub>7</sub> are high during this instruction.

# Q-BUS TIMING CARD - State Diagram

NOTE! CURRENT STATE INFORMATION IS TAKEN FROM PROM BUFFER REGISTER OUTPUT!

Fig. 4